# Directed Testing of ORAN using a Partially Specified Declarative Digital Twin

Alan Gatherer

Cirrus360

Dallas, USA

gatherer@cirrus3sixty.com

Chaitali Sengupta

Cirrus360

Dallas, USA

chaitali@cirrus3sixty.com

Sudipta Sen

Cirrus360

Dallas, USA

sudipta@cirrus3sixty.com

Jeffery H. Reed

Cirrus360 and Virginia Tech

Blacksburg, USA

reedjh@cirrus3sixty.com

Supported by NTIA PWSCIF under award 48-60-IF006

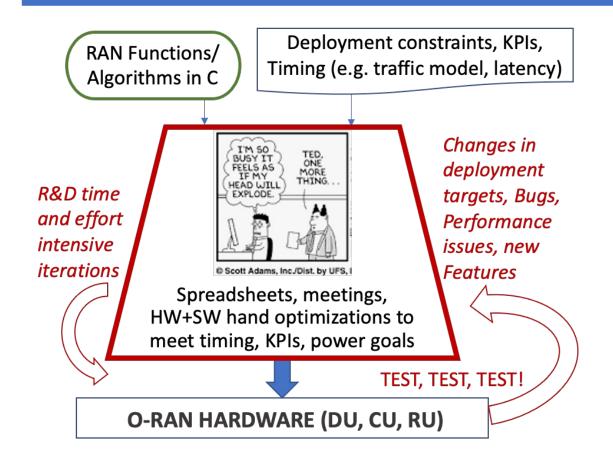

### Real time System Performance of RAN

A competitive high-availability (HA) RAN is a finely tuned real time system, operating near its capacity

Any mistiming of the hardware or software can lead to unexpected, hard-to-track, functional errors, e.g., buffer overflows, timing errors

Impacts energy efficiency AND performance

→ Requires automation, to direct testing towards specific HW/SW implementation & target deployment. But, not addressed by current open RAN testing strategies

### Why is Real Time System Testing Hard?

Complexities:

COTS HW/ cRAN/ vRAN,

multivendor,

partial knowledge,

deployment optimized solutions

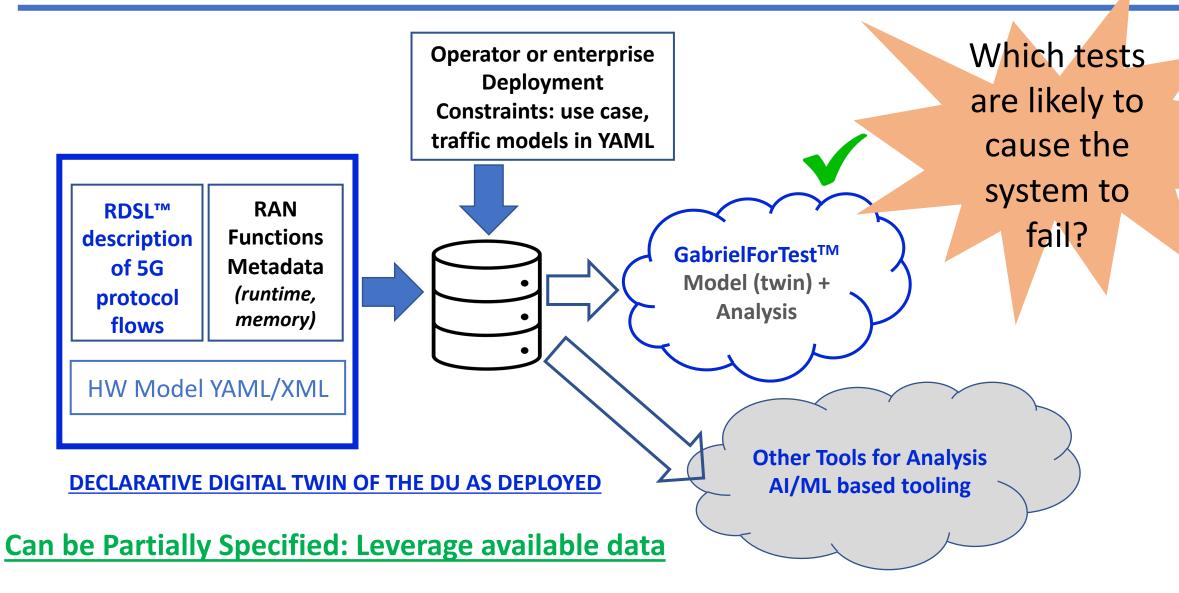

Which tests are likely to cause the system to fail?

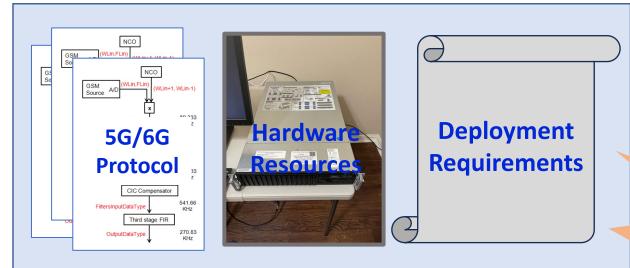

## A Declarative Digital Twin, powered by a RAN Domain Specific Language

### Domain Specific Language (RDSL™): At the heart of the Declarative Digital Twin

### **RDSL**

(.rdsl, Augmented with .yaml, .xml)

- Separate hardware and implementation independent description

- Declarative, Intent based → adding new requirements does not break the "twin"

- No vendor IP exposure

- Extensible, to meet future needs

- Simpler and formalized specification

- Automation of testing / digital twins

- ALSO:

- Automation of multi-vendor RAN integration

- Enable RIC apps by automating addition of KPIs

- Integrates smoothly with higherlevel automation and control

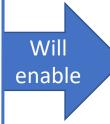

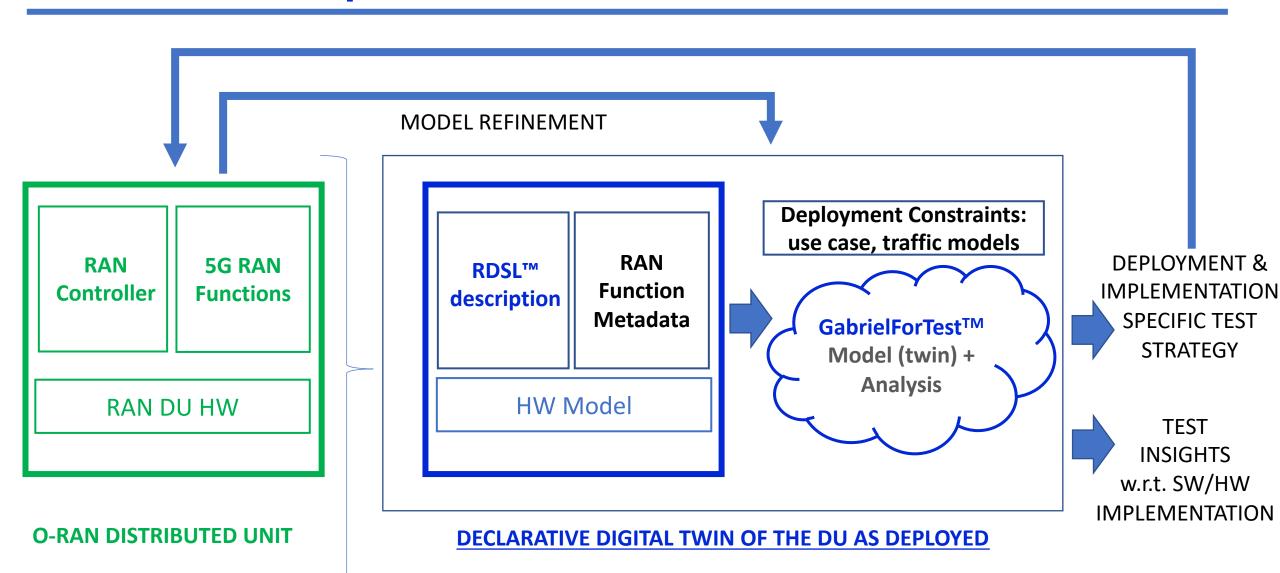

## A Declarative Digital Twin Approach to Testing Multi-vendor Open RAN Solutions

## How Cirrus360's Declarative Digital Twin works with industry standard testing solutions

## **Example input to the Declarative Digital Twin: How to test for Cache Sensitivity of DU running on COTS HW**

```

: stream[MAX_NUM_RX_ANT]{type = in}

srsIQSymbols

stream[AVG_NUM_SRS_UE]{type = in} % Maximum Number of UEs in a given SRS bandwidth

ueSpecific_srsInfo

stream[AVG_NUM_SRS_UE][MAX_NUM_RX_ANT][3]

error_streams_type1

stream[AVG NUM SRS UE][2]

error_streams_type2

%Internal Stream Definitions

stream[AVG_NUM_SRS_UE][MAX_NUM_RX_ANT]% These streams goes to non-RDSL domain

perUE srsChEst

%Flows Multi-instantiation of UE specific SRS Chest Flows for each Symbols

srsChestProc_perUE_perRxAnt_flow{i = 1:AVG_NUM_SRS_UE, j = 1:MAX_NUM_RX_ANT,

srsIQSymbols_perRxAnt_in = srsIQSymbols[j],

perUE_srsInfo_in = ueSpecific_srsInfo[i],

perUE_srsChEst_out = perUE_srsChEst[i][j],

error_s = error_streams_type1[i][j]}

description of DU Test Case: 10MHz Downlink-only

Based on fintel@iFlexRANTMReference Architecture

sendSrsChEst_to_MAC_flow{i = 1:AVG_NUM_SRS_UE,

perUE_srsChest_in = perUE_srsChEst[i],

perUE_srsInfo_in = ueSpecific_srsInfo[i],

error_s = error_streams_type2[i]}

```

```

apiVersion: rdsl/v0

kind: timing equation

metadata:

System=Constraints:

Speciming <= A*370 + B < 500

C: grid_period

A: num_ue1

B: gp_base

unit: clock

```

flow srsChest\_ueSpecific

```

r<pattern name="big_delay.c_0.L3_0.DDR_0.L3_0">

<defining memory>L3 0</defining memory>

<observing memory>L3 0</observing memory>

▼<exclusive define with>

<member>big delay.c 0.L3 0.DDR 0.L3 0</member>

<member>big delay.c 0.L3 0.DDR 0.accL3 0</member>

<member>pipeline.c 0.L3 0</member>

<member>L2toL2.c 0.L3 0.accL3 0</member>

</exclusive define with>

▶ <shares L2 II with>

</shares L2 II with>

▶ <shares L2 I0 with>

</shares L2 I0 with>

▶ <shares L2 OI with>

</shares L2 OI with>

▼<shares L2 00 with>

<member>big_delay.c_0.L3_0.DDR_0.L3_0

<member>big delay.c 0.L3 0.DDR 0.accL3 0

<member>L2toL2.c 0.L3 0.accL3 0</member>

<member>big delay.c 1.L3 0.DDR 0.L3 0</member>

<member>big delay.c 1.L3 0.DDR 0.accL3 0

<member>L2toL2.c 1.L3 0.accL3 0</member>

<member>big delay.c 2.L3 0.DDR 0.L3 0</member>

<member>big delay.c 2.L3 0.DDR 0.accL3 0

<member>L2toL2.c 2.L3 0.accL3 0/member>

<member>big delay.c 3.L3 0.DDR 0.L3 0

<member>big delay.c 3.L3 0.DDR 0.accL3 0</member>

<member>L2toL2.c 3.L3 0.accL3 0/member>

</shares L2 00 with>

<shares L3 II with/>

<shares L3 I0 with/>

<shares L3 OI with/>

<shares L3 00 with/>

▶ <can observe>

</can observe>

```

```

apiVersion: rdsl/v0

ind: SDK

name: NR5G1_DL_PDSCH_SYM

available patterns:

big_delay.c_0.L3_0.DDR_0.L3_0

big_delay.c_0.L3_0.DDR_0.accL3_0

big_delay.c_2.L3_0.DDR_0.accL3_0

pipeline.c_2.L3_0

L2toL2.c_2.L3_0.accL3_0

big_delay.c_3.L3_0.DDR_0.L3_0

big_delay.c_3.L3_0.DDR_0.accL3_0

pipeline.c_3.L3_0

L2toL2.c_3.L3_0.accL3_0

elementsize: 2000000

internalsize: 8000000

runtime: 7200

```

## Cache Sensitivity of DU running on COTS HW: Testing recommendations from Digital Twin

|    | Strategy                                                      | Latency (clock cycles)  | Result from GabrielForTest™                                                                                                                             |

|----|---------------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | No added constraints related to cache                         | 207,800                 | Test can successfully complete on a hardware slice of 4 cores well within available slot time                                                           |

| 2  | Cache eviction occurs for a set of small buffers (all < 10KB) | 239,400 (15% increase)  | Small impact, robust to this cache effect                                                                                                               |

| 3a | Large shared buffer (DL Config) eviction                      | 420,000 (102% increase) | Big impact! Requires this test scenario to<br>be reproduced on actual DU. May be a<br>candidate for code change to avoid this<br>situation in the field |

| 3b | Large data buffer cache eviction                              | 464,600 (124% increase) | Some additional impact, Digital Twin can explain why!                                                                                                   |

Table 1: Results for different pattern management (cache sensitivity) constraints: Impact on Latency

### **Conclusions**

- System Performance testing is hard! Takes expertise, R&D time, and effort but essential for multivendor ORAN to be competitive

- RDSL™ driven DECLARATIVE DIGITAL TWIN can accelerate system testing:

- Large repository of FACTS or CONSTRAINTS about the deployed ORAN component(s)

- That AUTOMATION can analyze for HW-SW implementation related corner cases

- Enables directed system testing to accelerate testing time and investment for ORAN

Contact: Chaitali Sengupta, <a href="mailto:chaitali@cirrus3sixty.com">chaitali@cirrus3sixty.com</a>, +1 214 733 2803

### **ADDITIONAL SLIDES**

#### **Team**

#### CHAITALI SENGUPTA (PhD), CEO

- Sr. Dir. Qualcomm, VP Eng. Reliance Jio India, Founder SNRLabs (startup), CTO SEVEN

- Distinguished Member Tech Staff Texas Instruments, Board Member Reliance Jio JV

- MIT Tech Review top innovators (TR35), 13 patent families

#### **ALAN GATHERER (PhD), CTO**

- Senior VP, 5G Baseband SoCs, Futurewei/Huawei (10 years rise to market leader)

- IEEE Fellow (1% of members), 90+ patents

- Texas Instruments Fellow, drove TI's domination for >10 years of 3G/4G

#### **SUDIPTA SEN, VP Product**

- VP Product Reliance Jio. Sr. Dir. Qualcomm. Tl. Shipped 100s million wireless products

- Founder SNRLabs, acquired by SEVEN. WiFi-cellular mobility product & core IP

Qualconn

#### PROF. JEFF REED, Advisor

- Virginia Tech, IEEE Fellow (Software Defined Radio)

- Co-founder of Federated Wireless, Advisor US spectrum policies